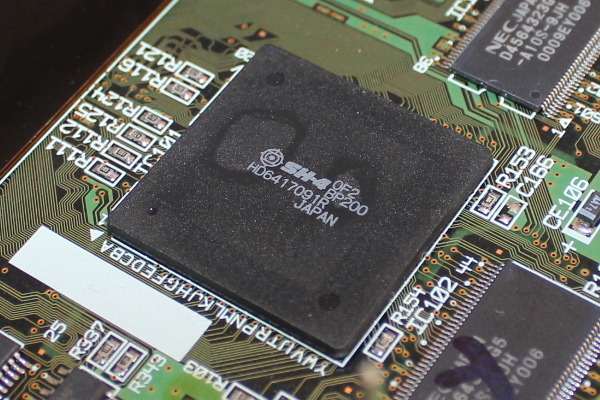

Desarrollado por: Hitachi

Modelo: SuperH-4 (SH-4)

Arquitectura: RISC

Frecuencia de reloj: 200 MHz

MIPS (Millones de Instrucciones Por Segundo): 360

Operaciones en coma flotante: 1,4 GFLOPS (precisión simple) a 128 bits

Canal de datos: 64 bits

Ancho de banda del canal de datos: 800 MB por segundo

Tecnología de fabricación: 250 nm

Caché:

- Instrucciones: 8 K

- Datos: 16 K